V roku 1977 bola VŠD premenovaná na Vysokú školu dopravy a spojov v Žiline (VŠDS). V roku 1996 sa zákonom č. 324/1996 Z. z. zmenil názov Vysokej školy dopravy a spojov na Žilinská univerzita v Žiline, ktorá následne rozširuje svoj profil z čisto technickej vysokej školy o prírodné vedy (od 18. augusta 1998), neskôr o humanitné vedy. V súčasnosti má univerzita sedem fakúlt:

- Fakulta prevádzky a ekonomiky dopravy a spojov (FPEDaS),

- Strojnícka fakulta (SjF),

- Fakulta elektrotechniky a informačných technológií (FEIT),

- Stavebná fakulta (SvF),

- Fakulta bezpečnostného inžinierstva (FBI),

- Fakulta riadenia a informatiky (FRI),

- Fakulta humanitných vied (FHV).

Univerzita sídli v univerzitnom kampuse Veľký diel, ktorý je postupne budovaný od 80. rokov 20. storočia. V centre mesta pôsobí Fakulta bezpečnostného inžinierstva, na letisku v Dolnom Hričove je pracovisko Katedry leteckej dopravy Fakulty prevádzky a ekonomiky dopravy a spojov a v Tatranskej Javorine pôsobí od roku 1999 Výskumný ústav vysokohorskej biológie.

Žilinská univerzita v Žiline je slovenská verejná vysoká škola univerzitného typu so sídlom v Žiline. Poskytuje vzdelanie v bakalárskych, inžinierskych/magisterských a doktorandských študijných programoch. Na tejto univerzite doteraz ukončilo štúdium takmer 90 000 absolventov, z toho 1 500 zahraničných. Spolu má univerzita vyše 1 500 zamestnancov a vo všetkých formách štúdia tu študuje približne 8 000 študentov v 169 akreditovaných študijných programoch.

Univerzita poskytuje ubytovanie študentom v študentských domovoch (internátoch) Veľký diel a Hliny V s kapacitou spolu cca 4 400 lôžok. Študenti majú možnosť stravovať sa v siedmich univerzitných výdajniach a bufetoch, prakticky na každom mieste výučby.

Fakulta elektrotechniky a informačných technológií Žilinskej univerzity v Žiline

Vznikla 1. októbra 1953 ako jedna z fakúlt Vysokej školy železničnej v Prahe. V roku 1960 bola spolu s celou univerzitou presťahovaná do Žiliny. V roku 1992 sa Strojnícka a elektrotechnická fakulta rozdelila na Strojnícku fakultu a Elektrotechnickú fakultu, v roku 2019 došlo k premenovaniu Elektrotechnickej fakulty na Fakultu elektrotechniky a informačných technológií.

Ako svoj príspevok k 70. výročiu vzniku Žilinskej univerzity v Žiline Fakulta elektrotechniky a informačných technológií pripravila v spolupráci so združeniami <tesla-piestany.sk> a <vuvt-zilina.sk> slávnostný seminár spojený s výstavou venovanou histórii výskumu, vývoja a výroby elektronických súčiastok na Slovensku, ktorá sa uskutočnila v priestoroch Rektorátu Žilinskej univerzity univerzitného kampusu Veľký diel. Ako uviedol v úvodnom príhovore dekan fakulty prof. Ing. Pavol Špánik, PhD., na fakulte študuje priemerne 1 100 študentov a 75 doktorandov. Fakulta tiež úspešne spolupracuje s priemyslom, napr. generálny riaditeľ slovenskej pobočky nadnárodnej spoločnosti ONSEMI v Piešťanoch Andrej Tomášik vo svojom prejave informoval, že fakulta realizuje pre ich spoločnosť výskumno-vývojové práce v objeme pol milióna eur ročne.

Vývoj a výroba elektronických súčiastok v TESLE Piešťany

Na výstave bolo umiestnených 14 veľkoplošných posterov o výrobe v TESLE Piešťany. 3D exponáty boli na výstave sústredené v samostatnej presklenej vitríne takto:

- katalógové listy a vzorky IO: MHB 1902 (SRAM 1 K 1 bit), MHB 5514 (SRAM 1 K 4 bit, MHB 2716 (EPROM 2 KB), MHB 4164 (DRAM 64 K 1 bit),

- katalógové listy a vzorky IO: MHB 8748 (8-bitový mikropočítač s EPROM a RAM), MHB 8708 (EPROM 1 KB), MHB 8155H (rozšírenie RAM a IO), MHB 8243 (rozšírenie IO),

- katalógové listy a vzorky IO: MHB 4116 (DRAM 16 K 1 bit), MHB 8080 (8-bitový mikroprocesor), MHB 8251 (USART), MHB 8255 (rozšírenie IO),

- zostava pre kanálový volič: elektrónky PCC 88 a PCF 82 a alternatívna polovodičová zostava – UHF tetródy KF 907 a párované varikapy 3 KB 105 G,

- zostava pre koncový stupeň riadkového rozkladu: elektrónky PL 504, PY 88, DY 86 a alternatívna polovodičová zostava – tyristor KT 119, rýchla dióda KY 189 a VN dióda KYX 36.

Výskum a vývoj bipolárnych polozákazníckych IO (PZIO) vo VÚVT Žilina

Projekt Hradlové pole HP 200

Vlastné hradlové pole bolo realizované tzv. ALS technológiou. Vstupný tranzistor bol rozdelený na dvojemitorové celky, ktoré bolo možné spojovať s cieľom získania hradiel s dvomi, štyrmi, šiestimi a ôsmimi vstupmi. Hradlá boli navrhnuté s otvoreným kolektorom na vytváranie spojových štruktúr AND. Z topologického hľadiska bol čip rozdelený na okrajovú časť s okrajovými zbernicami Ucc a GND a so vstupnými a výstupnými prevodníkmi, ktoré boli rovnomerne rozdelené po celom obvode čipu.

Vlastná hradlová matica sa nachádzala vnútri plochy čipu, vymedzenej vstupno-výstupnými prevodníkmi. Celkovo 240 hradiel bolo rozdelených do šiestich oblastí po 40 hradiel. Každý pás 40 hradiel bol napájaný zo samostatného stabilizátora napätia, umiestneného na konci pásu hradiel. Pás hradiel z oboch strán obopínajú dva rady vyhradených priestorov na prepojenie medzi hradlami v ose X v prvej metalickej úrovni. V centre matice medzi dvoma radmi priestorov na X prepojenia je vyhradený priestor na hlavnú zemniacu zbernicu. Ďalšie prepojenia medzi hradlami možno viesť v smere Y vo vyhradených priestoroch druhej metalickej úrovne.

Typické oneskorenie jedného vnútorného hradla bolo 2,5 ns, typické oneskorenie vstupného prevodníka bolo 2,0 ns a výstupného prevodníka 6 ns. Vonkajšie statické parametre zodpovedali parametrom integrovaných obvodov 74 ALS. Výrobnú realizáciu zabezpečoval k. p. TESLA Rožnov.

Projekt Testovací systém PZIO TADA 4

TADA 4 je určený na funkčné testovanie a meranie statických aj dynamických parametrov číslicových IO s maximálnym počtom vývodov 40. Tester je riadený personálnym počítačom PP 06.2. Základné vlastnosti TADA 4:

- umožňuje programový prechod z obvodu na obvod,

- umožňuje jednosmerné meranie aj dynamický funkčný test,

- umožňuje tvorbu dát na dynamické testovanie,

- má zabudované prostriedky na vnútornú diagnostiku,

- má kompaktnú konštrukciu, malé rozmery a nízku hmotnosť.

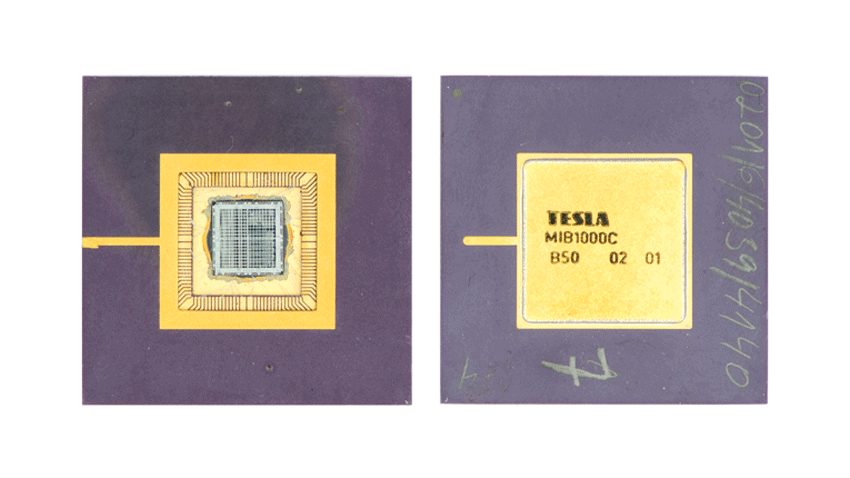

Projekt Hradlové pole HP 1000

Základný čip mal rozmery 7,55 x 7,25 mm a jeho prvá verzia sa montovala do keramického puzdra PGA 120. Obvod vyžadoval dve vonkajšie napájacie napätia (+5,0 V a +2,4 V) a dve uzemnenia, ktoré sa prepojovali až na doske plošných spojov na zvýšenie šumovej odolnosti. Vývody oboch uzemnení boli vedené cez osem pinov, napájanie +5,0 V bolo vyvedené cez štyri piny, napájanie +2,4 V cez osem pinov.

Po obvode čipu boli rozmiestnené vstupné a výstupné prevodníky. Vstupných prevodníkov bolo na čipe 92, využiteľných výstupných prevodníkov bolo cca 64. Vnútri čipu bolo vytvorených 32 stĺpcov v smere osi X a 34 radov v smere osi Y, čiže 1 088 vnútorných buniek, z ktorých bolo možné vytvoriť rôzne typy hradiel. Na čipe boli vytvorené tiež štyri zosilňovače hodinových impulzov na rozvod signálov s vysokým vetvením. Prepojenie hradiel a prevodníkov do logickej siete sa realizovalo v dvoch vrstvách metalizácie. Zákaznícky sa pritom navrhovali tri masky: jedna maska na prepojenia prevažne v smere X, druhá maska na prepojenia prevažne v smere Y a tretia maska na medzi vrstvové prepojenia.

K dispozícii boli základné funkčné prvky ako hradlá typu NAND, AND, AND – OR, vstupné a výstupné prevodníky a zosilňovače hodinových impulzov.

Projekt Testovací systém TADA 5, ktorý umožňoval:

- funkčné testovanie IO s maximálnym počtom testovaných pinov do 140, pričom každý pin mohol byť vstupný, výstupný alebo obojsmerný;

- dynamické testovanie IO s programovateľnou periódou testovania 160 ns až 128 µs; umožňoval tiež meranie jednosmerných parametrov, mal zabudovaný voltmeter na jednosmerné meranie s rozsahom 10 V alebo 1 V s rozlíšením 5 mV alebo 0,5 mV;

- jednoduchý návrh a odlaďovanie testov; mal HW nástroje na internú autodiagnostiku.

Riadiaci počítač mohol byť PP 06.2 alebo PC AT.

Prvý PZIO na báze HP 1000 vyvinutý vo VÚVT Žilina

MIB 1 000/0201 – obvod realizoval digitálne riadenie v uzavretej slučke servomotora na ovládanie pohonu na pohyb papiera v jednej súradnej osi, resp. na pohyb vozíka s kresliacim perom v druhej súradnej osi valcového kresliaceho zariadenia formátu A0 až A4, typ VZ 565 – CM 6426 alebo valcového kresliaceho zariadenia formátu A3, typ VZ 300. V riadení každého valcového kresliaceho zariadenia bol obvod použitý dvakrát – samostatne pre každú súradnicu jeden a vždy spolu s riadiacim mikroprocesorom typu 8086.

Vývoj a výroba hybridných integrovaných obvodov (HIO) v ZVT, závod Námestovo

Výroba pasívnych hrubovrstvových HIO

Z VUAP Praha bola do závodu ZVT Námestovo prevedená laboratórna výroba pasívnych hybridných integrovaných obvodov (HIO), založená na tzv. hrubovrstvovej technológii. Na keramickú doštičku sa sieťotlačou vodivou pastou vytvorila prepojovacia sieť a odporovými pastami sa vytvorili jednotlivé odpory (rezistory). Vytvorená prepojovacia sieť a rezistory sa potom vypaľovali za vysokej teploty. Rezistory sa v prípade potreby dostavovali na presnú hodnotu laserom. Po prípadnom predbežnom testovaní sa na vyrobené HIO nanášala ochranná pasivačná vrstva, realizovala sa potlač a prípadné finálne testovanie.

Výroba aktívnych hrubovrstvových HIO

Výroba aktívnych hrubovrstvových HIO bola realizovaná náročnejšou technológiou. Dá sa povedať, že išlo o kombináciu klasickej hrubovrstvovej technológie HIO, technológie SMT a technológie montáže čipov IO do keramických puzdier. Typicky sa touto technológiou realizovali HIO obsahujúce jeden alebo viac čipov IO, ktorých vývody sa pripájali profesionálnymi kontaktovačkami známymi z výroby IO v keramických puzdrách. Okrem čipov IO sa na keramickú podložku montovali aj čipy diód a rezistory a kondenzátory na montáž SMT.

Ing. Milan Gábik

združenie <tesla-piestany.sk>

združenie <vuvt-zilina.sk>